#include <env_period_registers_dae3.h>

Classes | |

| struct | veto_detail |

Protected Types | |

| typedef uint64_t | ppp_memory_t |

Static Protected Attributes | |

| static const std::string | env_period_policy_name = "DAE3EnvPeriodPolicy" |

| static const unsigned | FCOUNTR = 0x00 |

| raw frame count 32 bits More... | |

| static const unsigned | FCOUNTG = 0x04 |

| good frame count 32 bits More... | |

| static const unsigned | PCOUNTR0 = 0x08 |

| raw proton count low 32 bits More... | |

| static const unsigned | PCOUNTR1 = 0x0C |

| raw proton count high 16 bits More... | |

| static const unsigned | PCOUNTG0 = 0x10 |

| good proton count low 32 bits More... | |

| static const unsigned | PCOUNTG1 = 0x14 |

| good proton count high 16 bits More... | |

| static const unsigned | SCHPULSE = 0x18 |

| muon cerenkov pulses recived (only ion MS mode) More... | |

| static const unsigned | FIFOVETFRM = 0x100 |

| FIFO veto, number of frames vetoo. More... | |

| static const unsigned | SMPVETFRM = 0x104 |

| static const unsigned | INTVETFRM = 0x108 |

| Internal veto frame count (RO, 32 bit) period card only. More... | |

| static const unsigned | TS2PVETFRM = 0x110 |

| TS2 pulse veto. More... | |

| static const unsigned | WPULVETFRM = 0x114 |

| wrong pulse veto veto, number of frames vetoo More... | |

| static const unsigned | HZ50VETFRM = 0x118 |

| ISIS not at 50 Hz. More... | |

| static const unsigned | MSMVETFRM = 0x11C |

| ms mode vetoed frames More... | |

| static const unsigned | EXTPEROVFVC = 0x120 |

| external period overflow veto counter (RO) More... | |

| static const unsigned | EXT0VETFRM = 0x130 |

| static const unsigned | EXT1VETFRM = 0x134 |

| static const unsigned | EXT2VETFRM = 0x138 |

| static const unsigned | EXT3VETFRM = 0x13C |

| static const unsigned | FC0VETFRM = 0x150 |

| veto count More... | |

| static const unsigned | FC1VETFRM = 0x154 |

| veto count More... | |

| static const unsigned | FC2VETFRM = 0x158 |

| veto count More... | |

| static const unsigned | FC3VETFRM = 0x15C |

| veto count More... | |

| static const unsigned | FSDELAY = 0x200 |

| frame syn lower 18 bits 1us increments More... | |

| static const unsigned | FC0WINDLY = 0x204 |

| window delay More... | |

| static const unsigned | FC0WINWTH = 0x208 |

| window width More... | |

| static const unsigned | FC1WINDLY = 0x20C |

| window delay More... | |

| static const unsigned | FC1WINWTH = 0x210 |

| window width More... | |

| static const unsigned | FC2WINDLY = 0x214 |

| window delay More... | |

| static const unsigned | FC2WINWTH = 0x218 |

| window width More... | |

| static const unsigned | FC3WINDLY = 0x21C |

| window delay More... | |

| static const unsigned | FC3WINWTH = 0x220 |

| window width More... | |

| static const unsigned | FRAMETIME0 = 0x248 |

| low 32 bits More... | |

| static const unsigned | FRAMETIME1 = 0x24C |

| high 32 bits More... | |

| static const unsigned | RVETO = 0x40080 |

| veto enable register More... | |

| static const unsigned | RVFIFO = (1 << 0) |

| static const unsigned | RVSMP = (1 << 1) |

| static const unsigned | RVINT = (1 << 2) |

| static const unsigned | RVFCHOP0 = (1 << 3) |

| fast chopper 0, also bit 20 More... | |

| static const unsigned | RVTS2P = (1 << 4) |

| ts2 pulse veto More... | |

| static const unsigned | RVHZ50 = (1 << 6) |

| isis not at 50 Hz More... | |

| static const unsigned | RVMSM = (1 << 7) |

| ms mode More... | |

| static const unsigned | RVEXT0 = (1 << 12) |

| external veto 0 More... | |

| static const unsigned | RVEXT1 = (1 << 13) |

| external veto 1 More... | |

| static const unsigned | RVEXT2 = (1 << 14) |

| external veto 2 More... | |

| static const unsigned | RVEXT3 = (1 << 15) |

| external veto 3 More... | |

| static const unsigned | RVFCHOP1 = (1 << 21) |

| fast chopper 1 More... | |

| static const unsigned | RVFCHOP2 = (1 << 22) |

| fast chopper 2 More... | |

| static const unsigned | RVFCHOP3 = (1 << 23) |

| fast chopper 3 More... | |

| static const unsigned | RCONTROL = 0x40084 |

| run control More... | |

| static const unsigned | RCSTART = (1 << 0) |

| start data acquisition More... | |

| static const unsigned | RCFCLEAR = (1 << 1) |

| clear frame and veto counters More... | |

| static const unsigned | RCPCLEAR = (1 << 2) |

| clear proton counters More... | |

| static const unsigned | RCPERSZEQZERO = (1 << 3) |

| 0=external/harware periods, 1 = normal (start straight away) More... | |

| static const unsigned | RCEVENTMODE = (1 << 4) |

| enable event mode - send environment information to detector cards More... | |

| static const unsigned | RCFSSEL0 = (1 << 16) |

| frame sync select bit 0 More... | |

| static const unsigned | RCFSSEL1 = (1 << 17) |

| frame sync select bit 1 More... | |

| static const unsigned | RCFSSEL2 = (1 << 18) |

| frame sync select bit 2 More... | |

| static const unsigned | RCDELFSFIFORS = (1 << 14) |

| delay frame sync fifo reset out (assert and deassert) More... | |

| static const unsigned | RCRESET = (1 << 15) |

| reset run controller More... | |

| static const unsigned | RCFSENABLEOUT = (1 << 20) |

| frame sync enable out More... | |

| static const unsigned | RCFSSCH2 = (1 << 21) |

| frame sync schenchoff pulse (0=use first, 1=use second) More... | |

| static const unsigned | RCFSSEL = (RCFSSEL0 | RCFSSEL1 | RCFSSEL2) |

| static const unsigned | RCFSINT = (0) |

| 0 More... | |

| static const unsigned | RCFSSMP = (RCFSSEL0) |

| 1 More... | |

| static const unsigned | RCFSTOF = (RCFSSEL1) |

| 2 More... | |

| static const unsigned | RCFSMUONCK = (RCFSSEL0 | RCFSSEL1) |

| 3 muon cerenkov More... | |

| static const unsigned | RCFSMUONMS = (RCFSSEL2) |

| 4 muon MS mode More... | |

| static const unsigned | RCFSTOF1P = (RCFSSEL0 | RCFSSEL1 | RCFSSEL2) |

| 5 first isis ts1 pulse after ts2 gap (so 10hz) More... | |

| static const veto_detail | veto_details [] |

| static const unsigned | MAX_NUM_PERIODS = (16*1024) |

| should be same of OUTLUT and PERLUT sizes More... | |

| static const unsigned | MPCNT = 0x300 |

| Period card functionality. More... | |

| static const unsigned | MPLIM = 0x304 |

| main period (DAQ + Dwell) limit register (14 bit, RW) More... | |

| static const unsigned | PSCNT = 0x308 |

| period sequence counter (32 bit, RO) More... | |

| static const unsigned | PSLR = 0x30C |

| period sequence limit register (32 bit, RW) More... | |

| static const unsigned | PERINCTOT = 0x310 |

| total number of period increments (RO) More... | |

| static const unsigned | PEROUTDEL = 0x314 |

| period output delay in us (18 bit, RW) More... | |

| static const unused_t | LOOKTAR = UNUSED_REGISTER |

| lookup table access register (4bit, RW) - see below More... | |

| static const unsigned | PCREG = 0x40088 |

| period control register (16 bit, RW) - see below More... | |

| static const unsigned | ALT1SFV = 0x7FFF8 |

| Alt1 Sub Firmware version register (8bit, RO) More... | |

| static const unsigned | PERLUTSTART = 0x20000000 |

| period lookup table (16k x 32 bit RW) More... | |

| static const unsigned | PERLUTSIZE = (16*1024) |

| static const unsigned | PERLUTEND = (PERLUTSTART + 4*PERLUTSIZE) |

| static const unsigned | OUTLUTSTART = 0x22000000 |

| period switching output lookup table (16k x 32 bit RW) More... | |

| static const unsigned | OUTLUTSIZE = (16*1024) |

| static const unsigned | OUTLUTEND = (OUTLUTSTART + 4*OUTLUTSIZE) |

| static const unsigned | OUTLUTMASK = 0xffffffff |

| outlut is 32 bit More... | |

| static const unsigned | RFCNT0START = 0x24000000 |

| raw frame counters(16k x 32 bit, RW) in counts0 More... | |

| static const unsigned | RFCNT0SIZE = (16*1024) |

| static const unsigned | GFCNT0START = 0x25000000 |

| good frame counters(16k x 32 bit, RW) in counts0 More... | |

| static const unsigned | GFCNT0SIZE = (16*1024) |

| static const unsigned | RPCNT0START = 0x26000000 |

| raw proton counters(16k x 64 bit, RW) in counts0 More... | |

| static const unsigned | RPCNT0SIZE = (16*1024) |

| static const unsigned | GPCNT0START = 0x27000000 |

| good proton counters(16k x 64 bit, RW) in counts0 More... | |

| static const unsigned | GPCNT0SIZE = (16*1024) |

| static const unsigned | RPCNT1START = 0xffffffff |

| invalid address, not used More... | |

| static const unsigned | RPCNT1SIZE = 0 |

| static const unsigned | GPCNT1START = 0xffffffff |

| invalid address, not used More... | |

| static const unsigned | GPCNT1SIZE = 0 |

| static const unsigned | SPARE0START = 0xffffffff |

| invalid address, not used More... | |

| static const unsigned | SPARE0SIZE = 0 |

| static const unsigned | SPARE1START = 0xffffffff |

| invalid address, not used More... | |

| static const unsigned | SPARE1SIZE = 0 |

| static const unsigned | TARPERLUT = (1 << 0) |

| access PERLUT enable bit, RW More... | |

| static const unsigned | TAROUTLUT = (1 << 1) |

| access OUTLUT enable bit, RW More... | |

| static const unsigned | PCENDAFTER = (1 << 1) |

| end run after period sequence completes control bit (RW) More... | |

| static const unsigned | PCSEQCOMP = (1 << 2) |

| period sequence complete monitor bit (RO) More... | |

| static const unsigned | PCENDSEQCOMP = (1 << 3) |

| run ended and period sequence complete monitor bit (RO) More... | |

| static const unsigned | PCENAB = (1 << 4) |

| normal/period mode enable (RW) More... | |

| static const unsigned | PCEXTENAB = (1 << 5) |

| internal/external periods control mode enable (RW) More... | |

| static const unsigned | PCMULENAB = (1 << 6) |

| single/multi period sequence control mode enable (RW) More... | |

| static const unsigned | PCMULCOMP = (1 << 7) |

| multiple period sequence completed monitor bit (RO) More... | |

| static const unsigned | PCMSM = (1 << 11) |

| enable Muon MS mode More... | |

| static const unsigned | PCCLRPC = (1 << 13) |

| clear period counters (RW) need to assert & deassert More... | |

| static const unsigned | PCRESET = (1 << 15) |

| period card reset control bit(RW) need to assert & deassert More... | |

| static const unsigned | PERLUTTYPE = (1U << 31) |

| bit of perlut used to decide if dwell or daq period More... | |

Static Protected Attributes inherited from DAE3CardPolicy Static Protected Attributes inherited from DAE3CardPolicy | |

| static const int | FIRMVERS = 0x7FFFC |

| firmware version back end FPGA More... | |

| static const uint32_t | CARDSPACE = 0x28000000 |

| space allocated to a card More... | |

Additional Inherited Members | |

Public Member Functions inherited from DAE3CardPolicy Public Member Functions inherited from DAE3CardPolicy | |

| virtual | ~DAE3CardPolicy () |

Static Public Member Functions inherited from DAE3CardPolicy Static Public Member Functions inherited from DAE3CardPolicy | |

| static unsigned long | makeAddress (int position, unsigned long address) |

| static unsigned long | cardFromAddress (unsigned long address) |

| static unsigned long | baseAddress (unsigned long address) |

Static Public Attributes inherited from DAE3CardPolicy Static Public Attributes inherited from DAE3CardPolicy | |

| static const int | CRATE_MOD = 100 |

| should be same as DAE2CardPolicy::CRATE_MOD More... | |

| static const std::string | card_policy_name = "DAE3CardPolicy" |

| static const std::string | card_type = "DAE3" |

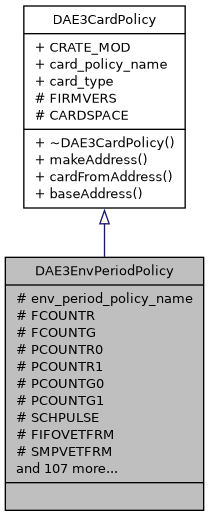

Detailed Description

Definition at line 4 of file env_period_registers_dae3.h.

Member Typedef Documentation

|

protected |

Definition at line 166 of file env_period_registers_dae3.h.

Member Data Documentation

|

staticprotected |

Alt1 Sub Firmware version register (8bit, RO)

Definition at line 141 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 7 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 27 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 28 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 29 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 30 of file env_period_registers_dae3.h.

|

staticprotected |

external period overflow veto counter (RO)

Definition at line 25 of file env_period_registers_dae3.h.

|

staticprotected |

veto count

Definition at line 32 of file env_period_registers_dae3.h.

|

staticprotected |

window delay

Definition at line 44 of file env_period_registers_dae3.h.

|

staticprotected |

window width

Definition at line 45 of file env_period_registers_dae3.h.

|

staticprotected |

veto count

Definition at line 33 of file env_period_registers_dae3.h.

|

staticprotected |

window delay

Definition at line 46 of file env_period_registers_dae3.h.

|

staticprotected |

window width

Definition at line 47 of file env_period_registers_dae3.h.

|

staticprotected |

veto count

Definition at line 34 of file env_period_registers_dae3.h.

|

staticprotected |

window delay

Definition at line 48 of file env_period_registers_dae3.h.

|

staticprotected |

window width

Definition at line 49 of file env_period_registers_dae3.h.

|

staticprotected |

veto count

Definition at line 35 of file env_period_registers_dae3.h.

|

staticprotected |

window delay

Definition at line 50 of file env_period_registers_dae3.h.

|

staticprotected |

window width

Definition at line 51 of file env_period_registers_dae3.h.

|

staticprotected |

good frame count 32 bits

Definition at line 11 of file env_period_registers_dae3.h.

|

staticprotected |

raw frame count 32 bits

Definition at line 10 of file env_period_registers_dae3.h.

|

staticprotected |

FIFO veto, number of frames vetoo.

Definition at line 18 of file env_period_registers_dae3.h.

|

staticprotected |

low 32 bits

Definition at line 55 of file env_period_registers_dae3.h.

|

staticprotected |

high 32 bits

Definition at line 56 of file env_period_registers_dae3.h.

|

staticprotected |

frame syn lower 18 bits 1us increments

Definition at line 39 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 153 of file env_period_registers_dae3.h.

|

staticprotected |

good frame counters(16k x 32 bit, RW) in counts0

Definition at line 152 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 157 of file env_period_registers_dae3.h.

|

staticprotected |

good proton counters(16k x 64 bit, RW) in counts0

Definition at line 156 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 161 of file env_period_registers_dae3.h.

|

staticprotected |

invalid address, not used

Definition at line 160 of file env_period_registers_dae3.h.

|

staticprotected |

ISIS not at 50 Hz.

Definition at line 23 of file env_period_registers_dae3.h.

|

staticprotected |

Internal veto frame count (RO, 32 bit) period card only.

Definition at line 20 of file env_period_registers_dae3.h.

|

staticprotected |

lookup table access register (4bit, RW) - see below

Definition at line 138 of file env_period_registers_dae3.h.

|

staticprotected |

should be same of OUTLUT and PERLUT sizes

Definition at line 119 of file env_period_registers_dae3.h.

|

staticprotected |

Period card functionality.

main period (DAQ + Dwell) counter (15 bit, bit 0-13 = number, 14 says if it is dwell) (RO)

Definition at line 128 of file env_period_registers_dae3.h.

|

staticprotected |

main period (DAQ + Dwell) limit register (14 bit, RW)

Definition at line 129 of file env_period_registers_dae3.h.

|

staticprotected |

ms mode vetoed frames

Definition at line 24 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 148 of file env_period_registers_dae3.h.

|

staticprotected |

outlut is 32 bit

Definition at line 149 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 147 of file env_period_registers_dae3.h.

|

staticprotected |

period switching output lookup table (16k x 32 bit RW)

Definition at line 146 of file env_period_registers_dae3.h.

|

staticprotected |

clear period counters (RW) need to assert & deassert

Definition at line 189 of file env_period_registers_dae3.h.

|

staticprotected |

normal/period mode enable (RW)

Definition at line 180 of file env_period_registers_dae3.h.

|

staticprotected |

end run after period sequence completes control bit (RW)

Definition at line 177 of file env_period_registers_dae3.h.

|

staticprotected |

run ended and period sequence complete monitor bit (RO)

Definition at line 179 of file env_period_registers_dae3.h.

|

staticprotected |

internal/external periods control mode enable (RW)

Definition at line 181 of file env_period_registers_dae3.h.

|

staticprotected |

enable Muon MS mode

Definition at line 187 of file env_period_registers_dae3.h.

|

staticprotected |

multiple period sequence completed monitor bit (RO)

Definition at line 183 of file env_period_registers_dae3.h.

|

staticprotected |

single/multi period sequence control mode enable (RW)

Definition at line 182 of file env_period_registers_dae3.h.

|

staticprotected |

good proton count low 32 bits

Definition at line 14 of file env_period_registers_dae3.h.

|

staticprotected |

good proton count high 16 bits

Definition at line 15 of file env_period_registers_dae3.h.

|

staticprotected |

raw proton count low 32 bits

Definition at line 12 of file env_period_registers_dae3.h.

|

staticprotected |

raw proton count high 16 bits

Definition at line 13 of file env_period_registers_dae3.h.

|

staticprotected |

period control register (16 bit, RW) - see below

Definition at line 139 of file env_period_registers_dae3.h.

|

staticprotected |

period card reset control bit(RW) need to assert & deassert

Definition at line 190 of file env_period_registers_dae3.h.

|

staticprotected |

period sequence complete monitor bit (RO)

Definition at line 178 of file env_period_registers_dae3.h.

|

staticprotected |

total number of period increments (RO)

Definition at line 132 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 145 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 144 of file env_period_registers_dae3.h.

|

staticprotected |

period lookup table (16k x 32 bit RW)

Definition at line 143 of file env_period_registers_dae3.h.

|

staticprotected |

bit of perlut used to decide if dwell or daq period

Definition at line 193 of file env_period_registers_dae3.h.

|

staticprotected |

period output delay in us (18 bit, RW)

Definition at line 137 of file env_period_registers_dae3.h.

|

staticprotected |

period sequence counter (32 bit, RO)

Definition at line 130 of file env_period_registers_dae3.h.

|

staticprotected |

period sequence limit register (32 bit, RW)

Definition at line 131 of file env_period_registers_dae3.h.

|

staticprotected |

delay frame sync fifo reset out (assert and deassert)

Definition at line 92 of file env_period_registers_dae3.h.

|

staticprotected |

enable event mode - send environment information to detector cards

Definition at line 86 of file env_period_registers_dae3.h.

|

staticprotected |

clear frame and veto counters

Definition at line 83 of file env_period_registers_dae3.h.

|

staticprotected |

frame sync enable out

Definition at line 94 of file env_period_registers_dae3.h.

|

staticprotected |

0

Definition at line 100 of file env_period_registers_dae3.h.

3 muon cerenkov

Definition at line 103 of file env_period_registers_dae3.h.

|

staticprotected |

4 muon MS mode

Definition at line 104 of file env_period_registers_dae3.h.

|

staticprotected |

frame sync schenchoff pulse (0=use first, 1=use second)

Definition at line 96 of file env_period_registers_dae3.h.

Definition at line 99 of file env_period_registers_dae3.h.

|

staticprotected |

frame sync select bit 0

Definition at line 88 of file env_period_registers_dae3.h.

|

staticprotected |

frame sync select bit 1

Definition at line 89 of file env_period_registers_dae3.h.

|

staticprotected |

frame sync select bit 2

Definition at line 90 of file env_period_registers_dae3.h.

|

staticprotected |

1

Definition at line 101 of file env_period_registers_dae3.h.

|

staticprotected |

2

Definition at line 102 of file env_period_registers_dae3.h.

5 first isis ts1 pulse after ts2 gap (so 10hz)

Definition at line 105 of file env_period_registers_dae3.h.

|

staticprotected |

run control

Definition at line 78 of file env_period_registers_dae3.h.

|

staticprotected |

clear proton counters

Definition at line 84 of file env_period_registers_dae3.h.

|

staticprotected |

0=external/harware periods, 1 = normal (start straight away)

Definition at line 85 of file env_period_registers_dae3.h.

|

staticprotected |

reset run controller

Definition at line 93 of file env_period_registers_dae3.h.

|

staticprotected |

start data acquisition

Definition at line 82 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 151 of file env_period_registers_dae3.h.

|

staticprotected |

raw frame counters(16k x 32 bit, RW) in counts0

Definition at line 150 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 155 of file env_period_registers_dae3.h.

|

staticprotected |

raw proton counters(16k x 64 bit, RW) in counts0

Definition at line 154 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 159 of file env_period_registers_dae3.h.

|

staticprotected |

invalid address, not used

Definition at line 158 of file env_period_registers_dae3.h.

|

staticprotected |

veto enable register

Definition at line 59 of file env_period_registers_dae3.h.

|

staticprotected |

external veto 0

Definition at line 70 of file env_period_registers_dae3.h.

|

staticprotected |

external veto 1

Definition at line 71 of file env_period_registers_dae3.h.

|

staticprotected |

external veto 2

Definition at line 72 of file env_period_registers_dae3.h.

|

staticprotected |

external veto 3

Definition at line 73 of file env_period_registers_dae3.h.

|

staticprotected |

fast chopper 0, also bit 20

Definition at line 64 of file env_period_registers_dae3.h.

|

staticprotected |

fast chopper 1

Definition at line 74 of file env_period_registers_dae3.h.

|

staticprotected |

fast chopper 2

Definition at line 75 of file env_period_registers_dae3.h.

|

staticprotected |

fast chopper 3

Definition at line 76 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 61 of file env_period_registers_dae3.h.

|

staticprotected |

isis not at 50 Hz

Definition at line 67 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 63 of file env_period_registers_dae3.h.

|

staticprotected |

ms mode

Definition at line 68 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 62 of file env_period_registers_dae3.h.

|

staticprotected |

ts2 pulse veto

Definition at line 65 of file env_period_registers_dae3.h.

|

staticprotected |

muon cerenkov pulses recived (only ion MS mode)

Definition at line 16 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 19 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 163 of file env_period_registers_dae3.h.

|

staticprotected |

invalid address, not used

Definition at line 162 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 165 of file env_period_registers_dae3.h.

|

staticprotected |

invalid address, not used

Definition at line 164 of file env_period_registers_dae3.h.

|

staticprotected |

access OUTLUT enable bit, RW

Definition at line 171 of file env_period_registers_dae3.h.

|

staticprotected |

access PERLUT enable bit, RW

Definition at line 170 of file env_period_registers_dae3.h.

|

staticprotected |

TS2 pulse veto.

Definition at line 21 of file env_period_registers_dae3.h.

|

staticprotected |

Definition at line 117 of file env_period_registers_dae3.h.

|

staticprotected |

wrong pulse veto veto, number of frames vetoo

Definition at line 22 of file env_period_registers_dae3.h.

The documentation for this class was generated from the following files:

- /isis2/instcontrol_temp/ICP/newicp/env_period_registers_dae3.h

- /isis2/instcontrol_temp/ICP/newicp/dae2_card.cpp

- /isis2/instcontrol_temp/ICP/newicp/env_period_card.cpp

1.8.5

1.8.5